Kupferflächen scheinen ein täuschend einfaches Thema zu sein. Doch die Verwendung erfordert sowohl elektrische als auch mechanische Überlegungen. Dieser Beitrag erklärt die mechanischen und fertigungstechnischen Aspekte von Kupferflächen für Leiterplattendesigner.

Der Begriff Kupferfläche sagt eigentlich alles: Man füllt einen Bereich mit Kupfer und hält dabei einen definierten Abstand zu anderen Kupferstrukturen ein. Die Kupferfläche kann an ein bestimmtes elektrisches Netz angeschlossen werden, um ein Signal in dem Bereich, den sie abdeckt, zu übertragen und zu verteilen. Normalerweise sind das Strom oder Masse; es kann aber auch jedes Signal sein. Andere Kupferstrukturen, die Teil desselben Netzes sind, sind mit der Kupferfläche verbunden, während der Rest nicht verbunden ist.

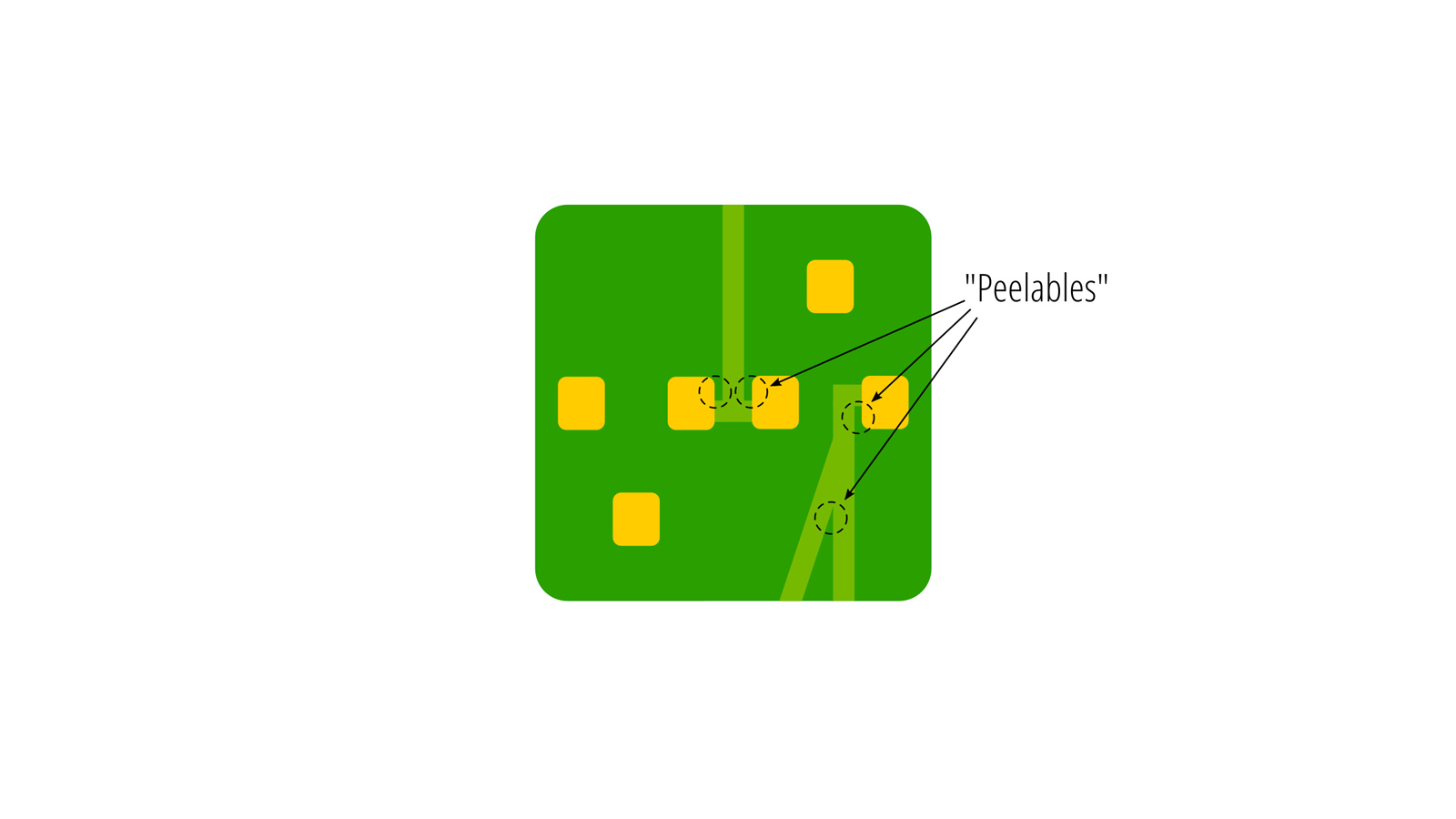

Kupfer ist ein guter Wärmeleiter, so dass jede lokale Erwärmung schnell über die Kupferfläche verteilt wird. Das bedeutet, dass sich Kupferflächen wie Wärmesenken verhalten. Das ist manchmal erwünscht, z.B. wenn man die Wärme von einem großen Masse-Pad eines Bauteils ableiten will. Aber die Wärmesenke ist unerwünscht, wenn man die Wärme beim Löten auf einem Pad halten will. Die gängigste Methode, diese Senke zu vermeiden, ist die Verwendung einer thermischen Entlastung, bei der Brücken oder Speichen zwischen dem Pad und der Füllung hinzugefügt werden, um die Wärmeableitung zu reduzieren. Auf diese Weise bleibt mehr Wärme lange genug im Pad, um das Löten einfacher, schneller und gleichmäßiger zu machen.

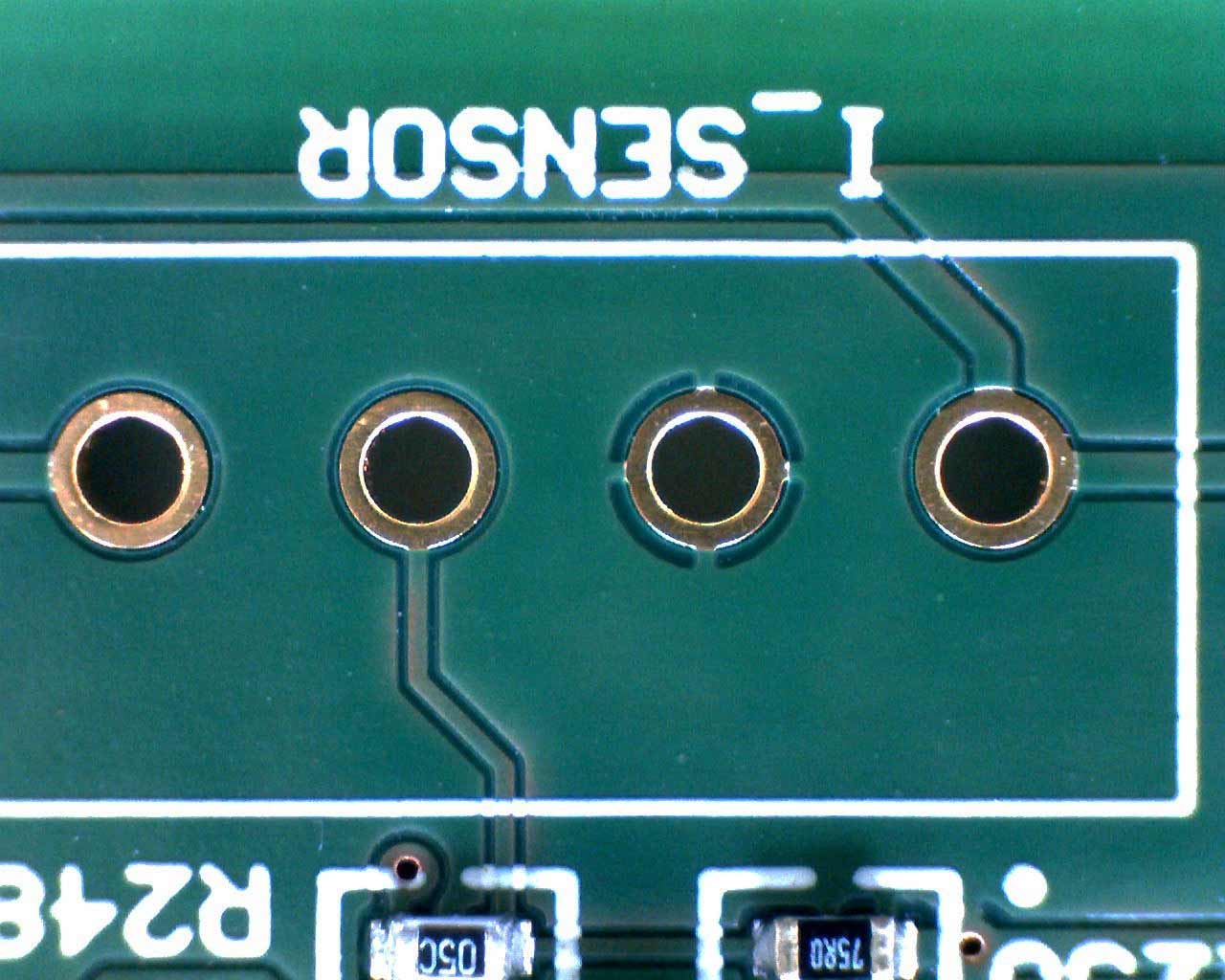

Das Pad links wird mit einer thermischen Entlastung versehen, um es mit der Kupferfläche zu verbinden. Das Pad auf der rechten Seite ist nicht verbunden.

Massive Kupferflächen sollten Standard sein

Design-Tools haben normalerweise zwei “Fülloptionen”: massiv oder schraffiert. Massive Kupferflächen sind am gebräuchlichsten. Denn die Berechnungen für Impedanz und Rückflusspfad sind einfach und sie verkomplizieren den Herstellungsprozess nicht, wie wir später noch besprechen werden. Eine massive Kupferfläche sollte unser Standard sein.

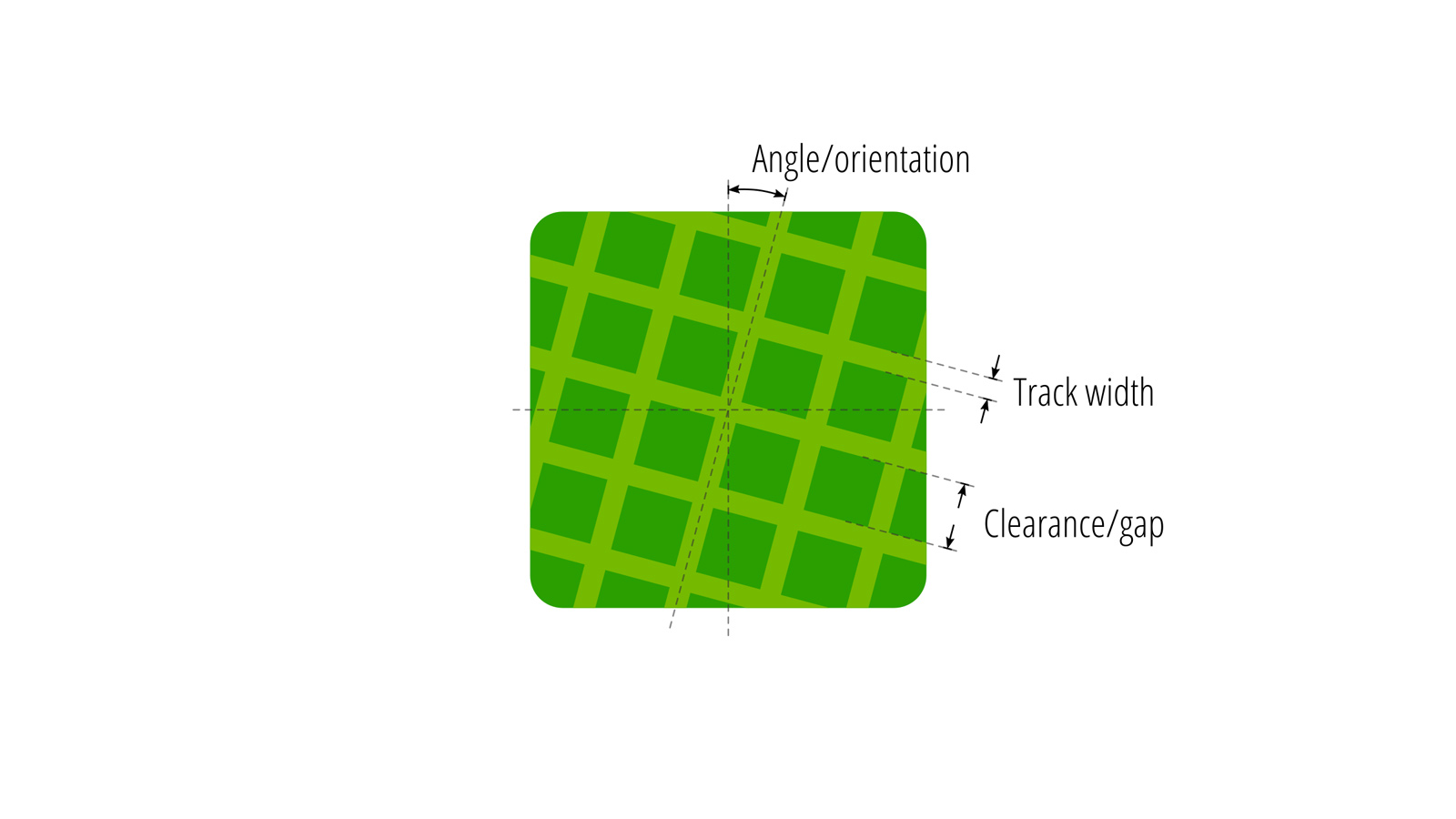

Ein schraffiertes Füllmuster auf einer Leiterplatte mit breiten Lücken, das den Spezifikationen von Eurocircuits entspricht.

In der Vergangenheit wurden schraffierte Kupferflächen oft benötigt, um das Haften von Kupfer, Harz und Lötstoppmaske auf dem Basismaterial zu unterstützen, damit sie während oder nach der Leiterplattenfertigung nicht “delaminieren”. Moderne Prozesse erfordern keine Schraffur für eine zuverlässige Leiterplattenfertigung. Darum braucht es schraffierte Kupferflächen nicht. Ausnahmen sind vielleicht einige der unten aufgeführten Fälle. Übrigens, wenn ein Fertiger eine Schraffur benötigt, prüfen Sie, ob er vielleicht sehr alte Geräte und Fertigungsprozesse verwendet.

- Einige Chip-Hersteller empfehlen ein schraffiertes Muster um kapazitive Touchpads.

- Schraffierte Flächen können bei sehr dünnen Leiterplatten mehr physikalische Flexibilität bieten.

- Kreative Signalintegritätsübungen unter besonderen Umständen z.B. sehr dünne Leiterplatten oder exotische Substrate können ein nicht festes Muster erfordern.

- Schraffierte Kupferflächen reduzieren die Kupferdichte auf der Leiterplatte, um mehr vom Substrat freizulegen, was manchmal zum Ausgleich des Kupfers erforderlich sein kann. Ein guter Hersteller sollte in der Lage sein, Euch zu sagen, ob Teile Eures massiven Musters aus diesem Grund durch ein schraffiertes ersetzt werden sollten.

- Wenn Ihr eine schöne Schaltung entwerft, kann eine Schraffur oder sogar ein aufwändigeres Muster eine Voraussetzung für den visuellen Effekt sein. Sprecht in diesem Fall mit Eurem freundlichen Leiterplattenhersteller, ob er das fertigen wird und informiert Euch über die Einschränkungen, an die Ihr Euch halten müsst; nicht alles ist möglich.

Es gibt wahrscheinlich noch mehr Fälle, doch die sind möglicherweise noch esoterischer. Bleibt also bei einer massiven Kupferfläche! Es sei denn, Ihr könnt ein anderes Muster wirklich rechtfertigen. Und wie immer lohnt es sich, frühzeitig mit dem Hersteller zu sprechen, was realisierbar ist. Nebenbei bemerkt, die nächste Version von KiCad, v6, enthält eine Option für eine schraffierte Kupferfüllung. Lasst Euch nicht in Versuchung bringen!

Das Problem mit Schraffierungen und anderen Mustern

Schraffierte Kupferflächen oder Gittermuster bereiten den Leiterplattenherstellern Kopfzerbrechen. Der Grund ist, dass die von uns eingereichten Daten vor der Weitergabe an die Fertigung einer Vielzahl von Prüfungen unterzogen werden. Die Gitter machen einige dieser Prüfungen deutlich anspruchsvoller und zeitaufwändiger als massive Kupferflächen.

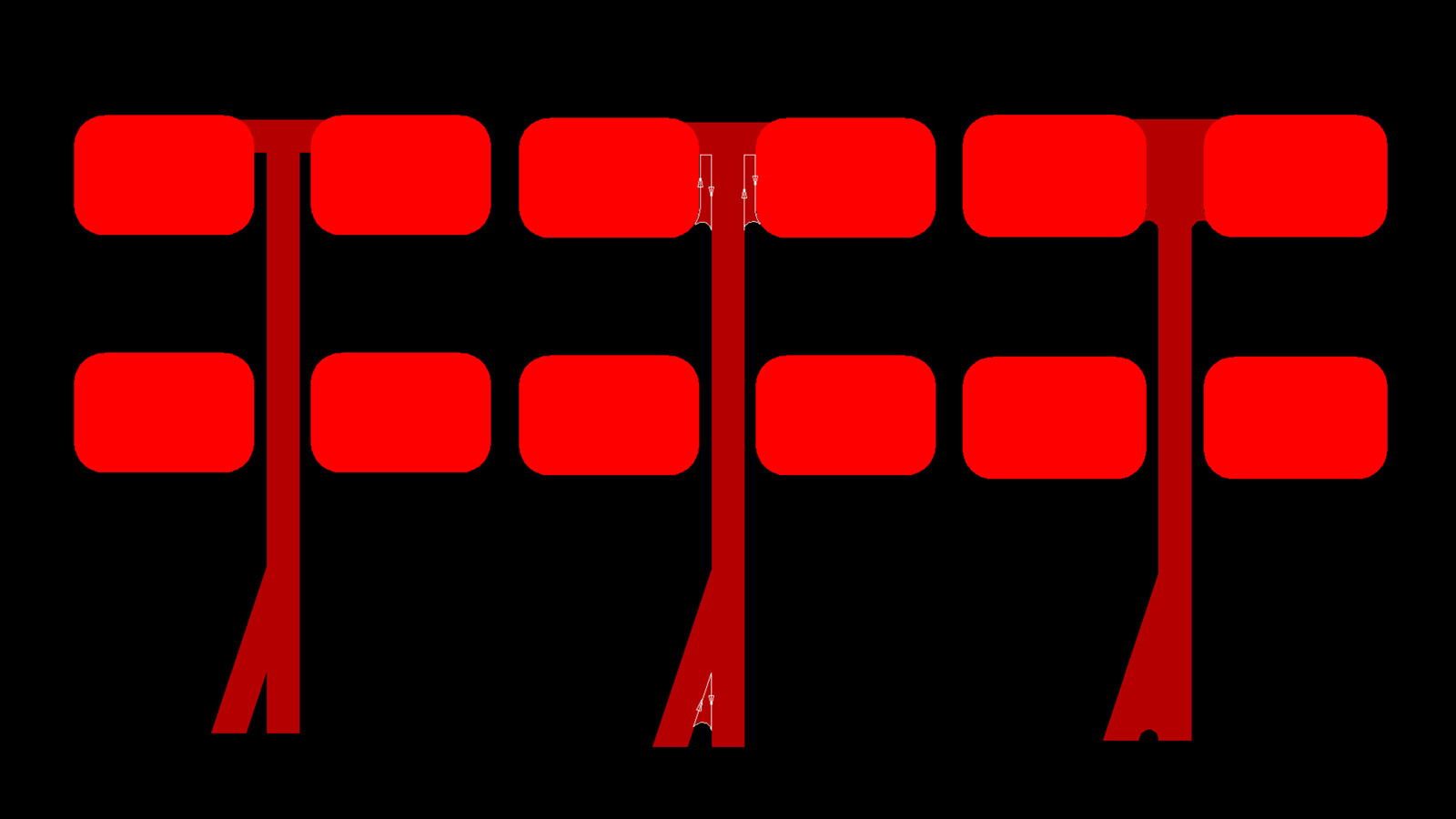

Ablösungen sind winzige Lücken, die durch netzgleiche Verbindungen verursacht werden. Sie können dazu führen, dass trockene Foliensplitter abfallen und sich an anderer Stelle wieder anlagern und Kurzschlüsse erzeugen.

Ablösungen (nicht zu verwechseln mit Abziehlack) sind Bereiche, in denen Merkmale desselben Netzes einen kleinen Splitter oder eine Ecke bilden. Während der Fertigung bedeckt der Leiterplattenhersteller die Bereiche des Kupfers, die abgezogen werden sollen, mit einem Trockenresist. Dann beschichtet er die Leiterplatten mit elektrolytischem Kupfer und Zinn und ätzet sie in Behandlungsbädern. In diesem nasschemischen Prozess können sich winzige Teile des Trockenresist ablösen, umherschweben und sich an anderer Stelle auf der Leiterplatte ablagern. Das führt zu Kurzschlüssen, Unterbrechungen und Fehlstellen. Um dies zu verhindern, suchen wir nach ablösbaren Teilen und reparieren sie. Nur: bei einem schraffierten Muster kann es viel mehr Ablösungen geben als üblich.

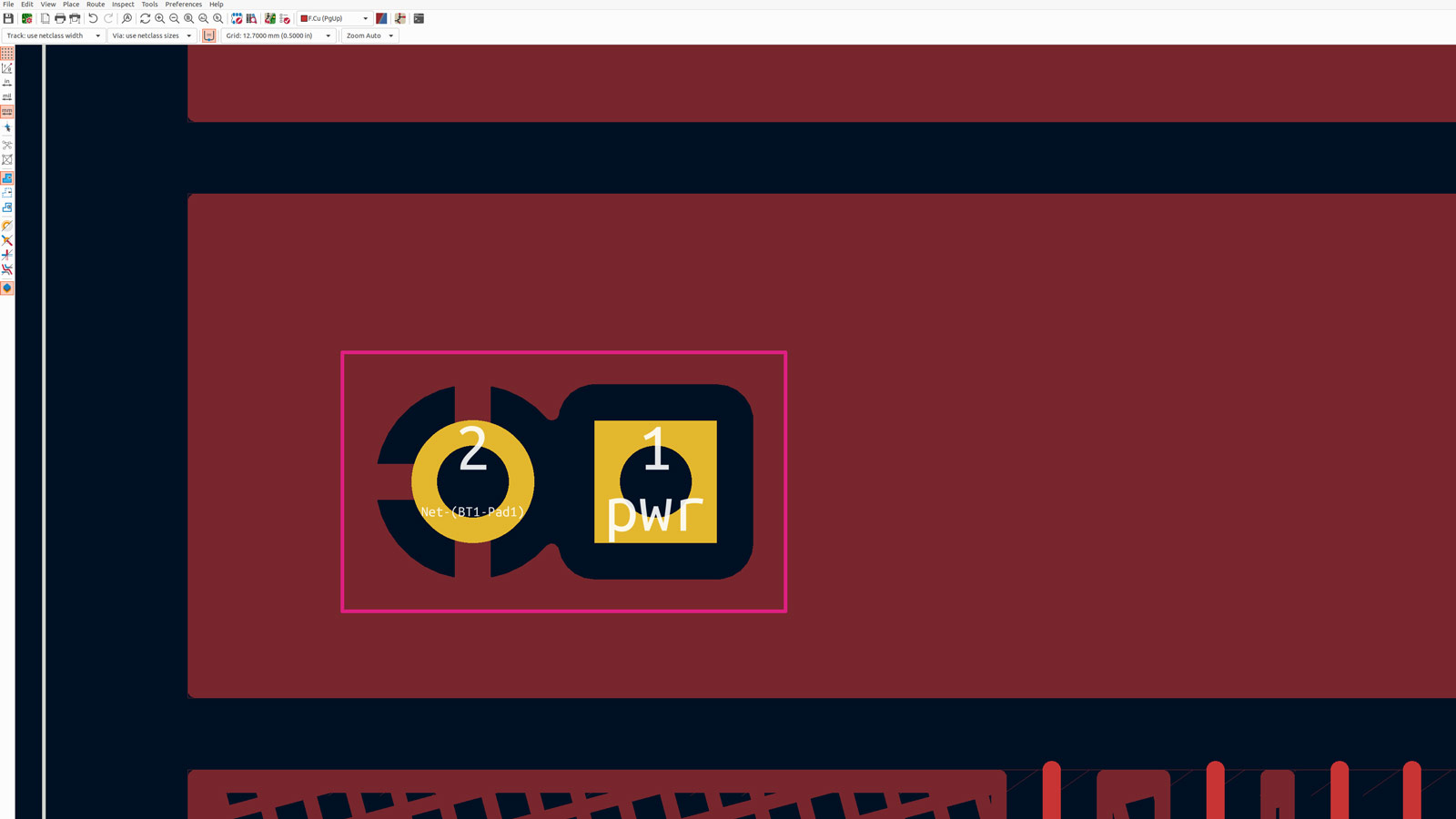

Das ursprüngliche Design (links) hat ein “ablösbares” Problem, das identifiziert (Mitte) und behoben wurde (rechts)..

Pinholes (kleine Fehlstellen) sind winzige Öffnungen in den Daten einer Kupferfläche. Dadurch werden kleine Fehlstellen im Trockenresist erzeugt. Verursacht wird dieser Effekt oft durch Design-Tools, die gefüllte Flächen mit gezeichneten Linien oder Polygonen darstellen. Durch Ablösen während der Galvanisierung können die Resistrückstände Probleme verursachen, weil sie herumschweben und sich irgendwo auf der Leiterplatte wieder absetzen. Wir suchen diese Öffnungen und beheben diese Fehlstellen in dem wir vollständig geschlossen Kupferflächen erstellen. Und, wie schon erklärt, haben Schraffierungen bzw. Gitter das Potenzial, viele Fehlstellen zu erzeugen, im Gegensatz zu vollständig geschlossenen Kupferflächen.

Ein allgemeiner DRC (Design Rule Check) auf einer schraffiert gefüllten Leiterplatte ist sehr anspruchsvoll zu verifizieren. Verletzungen des Strichspurabstandes sind für die Werkzeuge leicht zu finden. Viel schwieriger bis unmöglich zu finden sind sie aber, wenn sie innerhalb einer einzelnen Form auftreten. Ein Beispiel dafür ist das, was wir als Kupferschnitte bezeichnen: winzige Verbindungen zwischen zwei großen, netzgleichen Kupferstrukturen, die keine Leiterbahn sind. Wenn wir diese winzigen Verbindungen nicht erkennen und beheben, werden sie überätzt und verschwinden.

Das Erkennen und Reparieren potenzieller Probleme mit schraffierten Kupferflächen ist zwar möglich, kostet aber Bearbeitungszeit der CAM-Software und Zeit für die Ingenieure, die sie bedienen und überwachen. Das erhöht natürlich die Produktionskosten. Einen Teil dieser höheren Kosten gibt der Hersteller an den Kunden weiter, aber die primäre Auswirkung für den Kunden sind Verzögerungen beim Verarbeiten der Daten und der anschließenden Reparatur. Letztendlich ist ein gutes Design über mehrere Leiterplattenhersteller hinweg konsistent reproduzierbar. Mit schraffierten Kupferflächen lässt sich das nicht sicherstellen, weil zu viele unerwünschte Variationen auftreten.

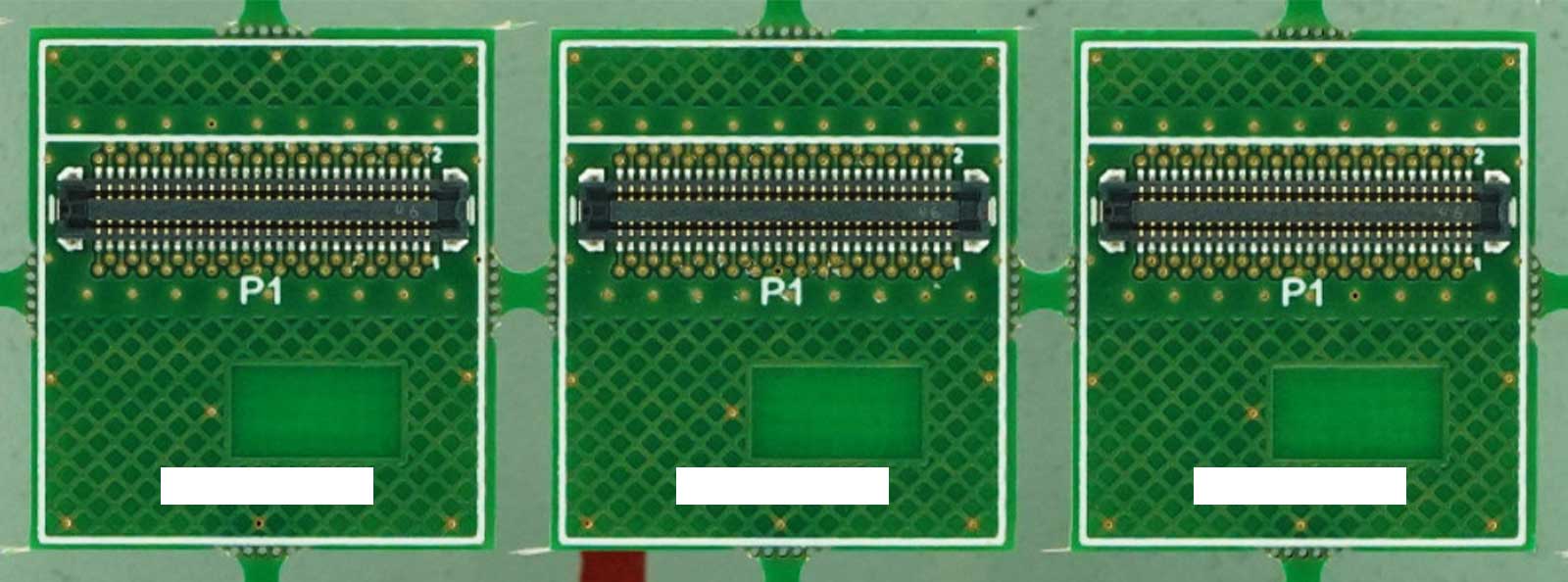

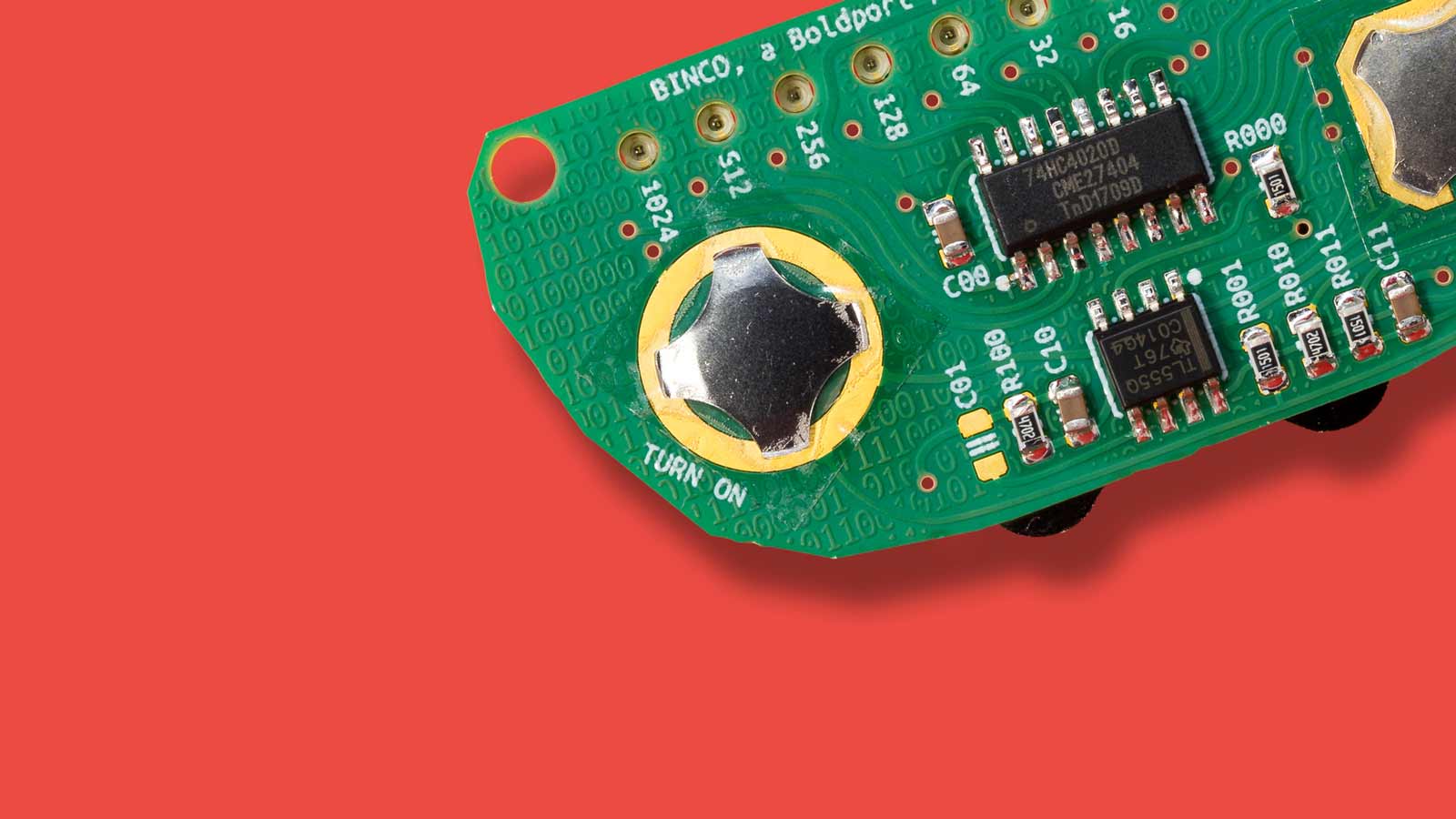

Das ist BINCO, eines meiner Projekte, das Eurocircuits hergestellt hat. Die Einsen und Nullen füllen machten die Dateien riesig und komplex. Das führte so weit, dass der Visualizer nach ein paar Stunden abgeschaltet hat. Eurocircuits war so freundlich, mir all die Probleme, von denen ich jetzt weiß, zu verschweigen und mir nicht mehr dafür zu berechnen.

Wie Eurocircuits Weg beim Design von Kupferflächen hilft

Wenn Ihr eine Leiterplatte bei Eurocircuits bestellt, dann stellen wir sicher, dass sie zuverlässig gefertigt werden kann. Wir tun viel, um Euch so schnell wie möglich qualitativ hochwertige Boards zu fertigen und zu liefern. Aus diesem Grund korrigieren wir kritische Stellen in den Daten, von denen wir wissen, dass sie Probleme verursachen können, wie z.B. Ablösungen, Pinholes und Kupferschnitte. Leider treten diese unerwünschten Effekte bei dichten Gitterstrukturen viel häufiger auf, als bei anderen Kupferflächen.

Selbstverständlich fertigt Eurocircuits schraffierte Kupferflächen, wenn Euer Design es erfordert. Die Gittermuster müssen jedoch eine Mindestgröße erfüllen, die in den PCB-Designrichtlinen für Kupferflächen erklärt sind.

Wenn das Gitter diese Mindestanforderungen nicht erfüllt, wird es in eine massive, vollflächige Kupferfüllung umgewandelt.

Hier findet Ihr weitere Informationen zu diesem Thema:

PCB Designrichtlinien – Kupferlagen

- Der Ätzprozess in der Leiterplattenfertigung

https://www.eurocircuits.de/38-innenlagen-belichtung/

Das ist der sechste Beitrag einer sechsteiligen Serie, in der Saar Drimer, Elektronikdesigner und technischer Redakteur bei Eurocircuits, über fertigungsgerechtes Design (Design for manufacturing) schreibt: Außenkontur (Outline), Sicherheitsabstände von Bauteilen (Courtyards), Restringe (Annular Rings), Sperrflächen (Keepouts), Passermarken (Fiducials) und Kupferflächen (Copper Fills).