Das Leiterplattendesign mit Ball-Grid-Array-Gehäusen (BGAs) kann knifflig sein; die Fertigung manchmal sogar noch schwieriger. In diesem Blog erörtert Saar Drimer, Entwickler und Technischer Redakteur, was beim Entflechten von BGA-Layouts zu beachten ist, damit die Leiterplatten einfacher und oft auch kostengünstiger hergestellt werden können.

Alle Zahlen in diesem Artikel entsprechen dem Stand zum Zeitpunkt der Erstellung dieses Artikels. Die aktuellen Bedingungen finden Sie auf unserer Seite Klassifizierung.

Fertigungskosten steigen mit der Komplexität

Wir wissen, dass eine Leiterplatte umso teurer werden kann, je dünner, kleiner und enger die Leiterbahnen, Pads, Löcher usw. werden. Die Miniaturisierung bedeutet auch, dass immer weniger Hersteller in der Lage sind, uns diese Möglichkeiten überhaupt oder zu einem erschwinglichen Preis anzubieten. Das bedeutet, dass es im Allgemeinen in unserem Interesse ist, das Leiterbild so “groß” wie möglich zu halten.

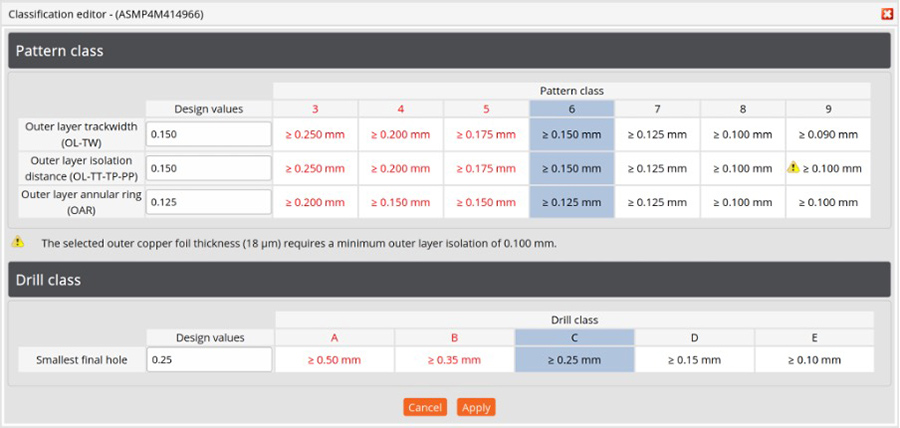

Wir verwenden “Leiterbildklassen (pattern classes)” und “Bohrklassen (drill classes)” als einfache Einordnung der Produzierbarkeit der Leiterplatte.

Unsere erste Aufgabe ist es, von unserem Leiterplattenhersteller herauszufinden, welche Einschränkungen er bei der Fertigung hat und wo seine Preisgrenzen liegen. Es gibt zwei Hauptgründe, warum das eine gute Idee ist.

Erstens werden wir nichts entwerfen, was nicht herstellbar ist: entweder verstößt es gegen Designregeln oder es ist zu teuer. Zweitens würden wir keine Energie darauf verwenden, ein Design mit “großen” Leiterbildern zu entwerfen, nur um dann festzustellen, dass es genauso viel kostet wie die Herstellung eines Designs mit “kleinerem” Leiterbild.

Bei Eurocircuits haben wir ein einfaches Klassifizierungssystem, mit dem sich all dies leicht herausfinden lässt: Die Leiterbildklassen (Pattern Classes) 3 bis 9 und die Bohrklassen (Drill Classes) A bis E geben jeweils die Mindestgröße an, die die Klassifizierung der Leiterplatte für Leiter bzw. Bohrungen bestimmt. Um die Gesamtklassifizierung einer Leiterplatte zu ermitteln, werden die Leiterbild- und Bohrklassen kombiniert, z.B. 3A, 5D oder 8E.

Der Preisunterschied zwischen den Klassen ist nicht linear. Manchmal gibt es keinen Preisunterschied zwischen den Klassen. Er hängt von den Einzelheiten der Bestellung ab; in der Regel gilt die Größe der Gesamtfläche der Bestellung: Leiterplattengröße multipliziert mit der Menge.

Sie können unsere Preisunterschiede für jede beliebige Leiterplattenkonfiguration mit unserem Visualizer ermitteln; im Allgemeinen ist jedoch 6C bei geringeren Stückzahlen der günstigste Punkt und ist auch unsere Standardeinstellung. Es ist auch gut zu wissen, dass wir zwar Leiterplatten der Klasse 9E herstellen können, dies aber keine Pooling-Option ist, so dass es einen großen Preissprung zwischen 8E und 9E gibt.

Das große Spektrum der BGA-Bauformen

Einige Bauteile sind in mehreren Gehäuseformen erhältlich, andere nur in einer. Manchmal haben wir auf der Platine Platz für große Gehäuse, manchmal nicht. In der Regel ist es eine gute Idee, ein Design mit dem größtmöglichen Gehäuse mit dem geringsten Fine-Pitch zu beginnen. Dies macht die Fertigung oft billiger und einfacher. Außerdem ermöglicht es uns auch, auf eine kleinere B umzusteigen, wenn es nötig ist, was man von der umgekehrten Vorgehensweise nicht immer behaupten kann.

Auch wenn wir sie alle als BGAs bezeichnen, gibt es viele verschiedene BGA-Technologien, und innerhalb jeder dieser Technologien gibt es viele Varianten. Die potenziellen Herausforderungen beim Design in einem bestimmten Gehäuse hängen von mehreren Faktoren ab: Pitch, Pad-Größe, Lötstoppmasken-Öffnungen, Pin-Anordnung und die anwendungsspezifische Verwendung der Pins.

Die Anzahl der Kombinationen dieser Variablen ist so groß, dass es unpraktisch ist, Designregeln oder absolute Aussagen darüber zu treffen, was möglich ist und was nicht. Das gilt für jeden Leiterplattenhersteller. Stattdessen werden wir darauf hinweisen, welche Constraints wir berücksichtigen müssen und worauf wir beim Platzieren der Bauteile und beim Routing achten sollten.

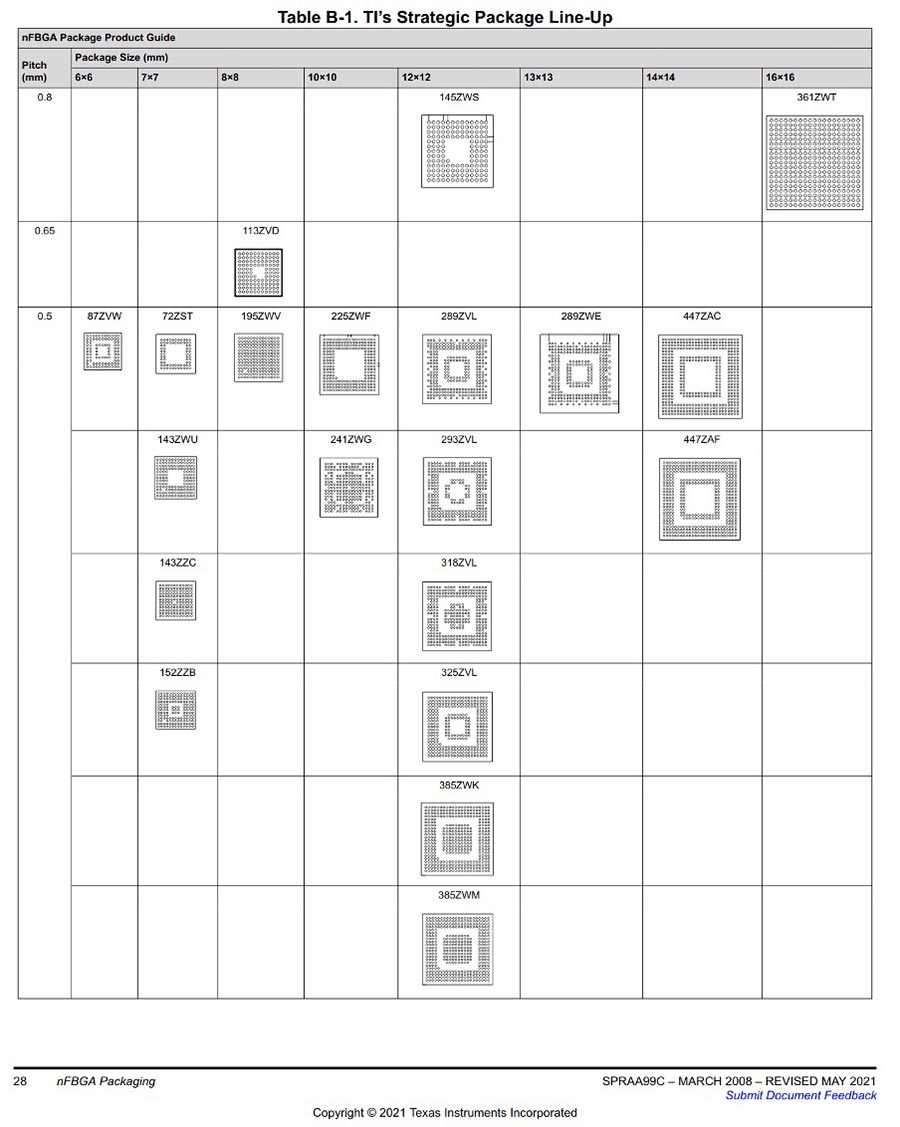

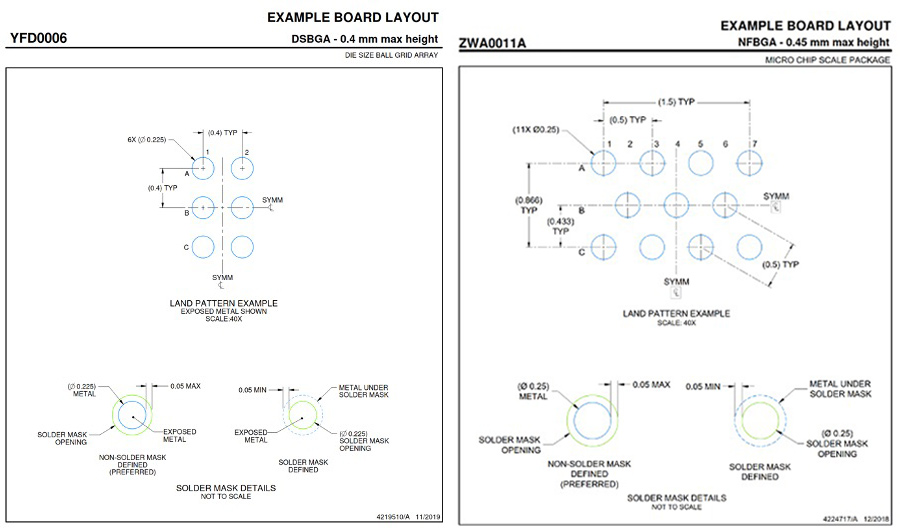

Eine Auswahl aus einem Typ der von TI angebotenen BGA-Gehäuse. Es gibt beträchtliche Variationen bei der Platzierung der Anschlüsse, hauptsächlich um das Fanout einzelner Signale zu erleichtern. Aufgrund dieser Vielzahl von Variationen bei allen BGA-Technologien und Pin-Anordnungen gibt es keine Regeln, die für alle gelten.

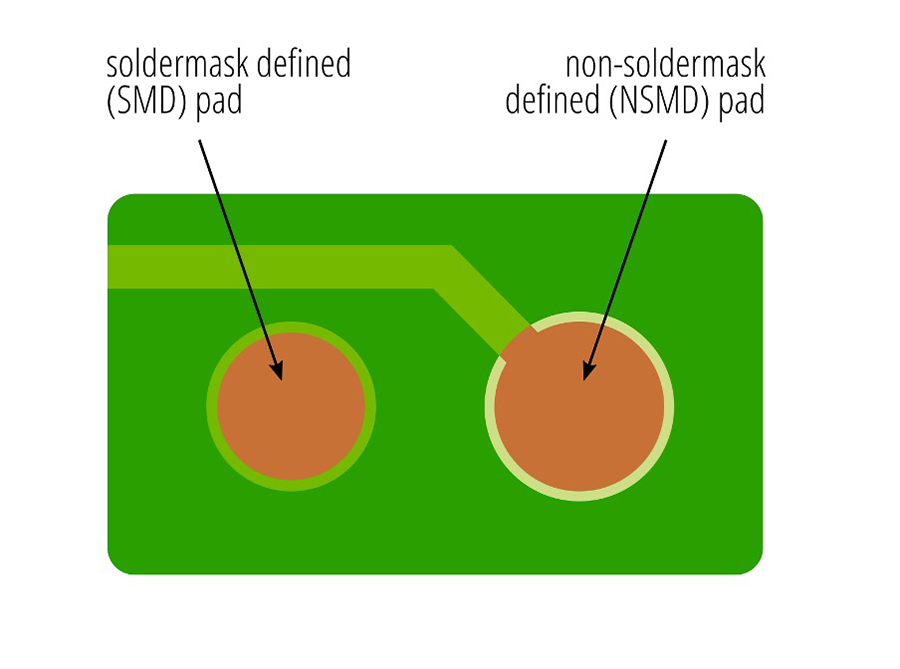

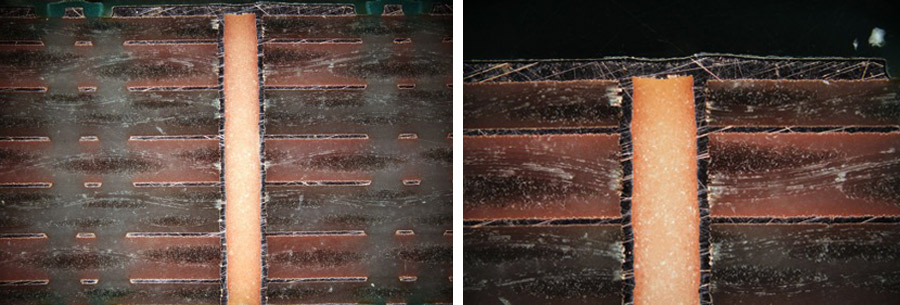

Lötstopplack-definiertes Pad (SMD) auf der linken Seite und nicht-lötstopplack-definiertes Pad (NSMD) rechts.

Bevor wir fortfahren, sollten wir uns mit einer weiteren Sache vertraut machen. Die Hersteller geben oft zwei Arten von möglichen BGA-Pads an: Non-SolderMask-Defined oder SolderMask-Defined (NSMD bzw. SMD, was übrigens eine unglückliche Wahl der Akronyme ist). Kurz gesagt bedeutet lötstoppmasken-definiert, dass die Lötstoppmaskenöffnung kleiner als das Kupferpad ist, und nicht lötstoppmasken-definiert, dass die Lötstoppmaskenöffnung größer als das Kupferpad ist. Jede der beiden Varianten hat anwendungsspezifische Vor- und Nachteile, aber NSMD scheint im Allgemeinen von Bauteil- und Leiterplattenherstellern bevorzugt zu werden.

Überlegungen beim Entflechten des BGA-Layout

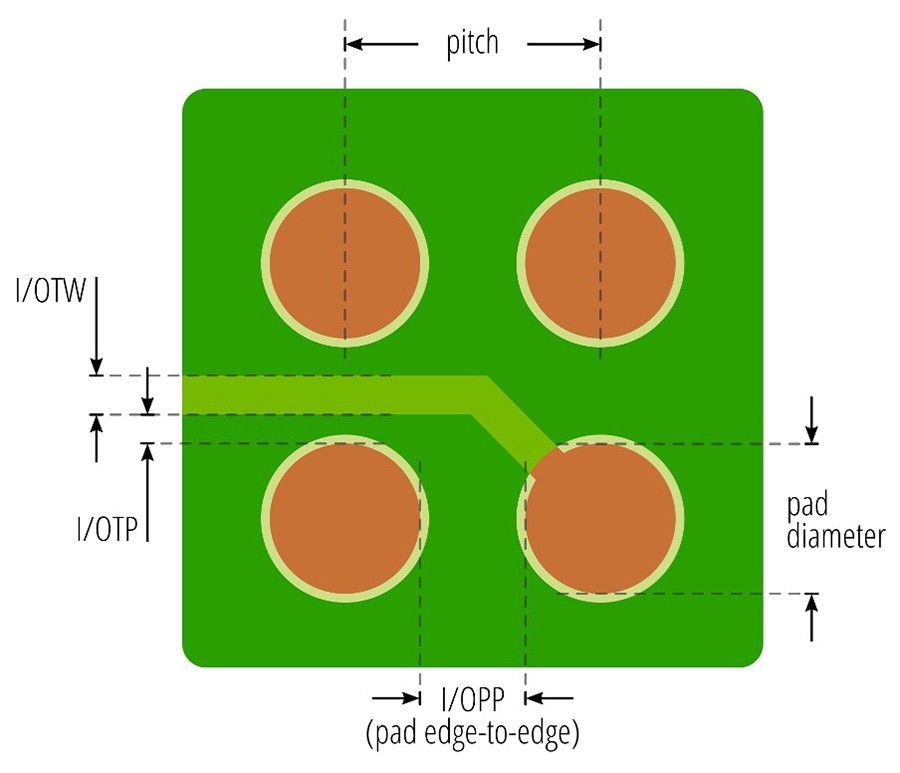

Pitch ist der Abstand zwischen den Mittelpunkten der Lötpads; I/OTW ist die innere/äußere Leiterbahnbreite; I/OTP ist die innere/äußere Leiterbahn-zu-Pad-Abstand; und I/OPP ist der innere/äußere Pad-zu-Pad-Abstand.

Inzwischen haben wir die entsprechenden Informationen vom Leiterplattenhersteller. Unsere nächste Aufgabe besteht darin, das Datenblatt des Bauteils und die zugehörigen Anwendungshinweise zu prüfen. Wir suchen mindestens nach den folgenden Informationen:

- empfohlene Grundfläche und Pad-Größe für SMD- und NSMD-Techniken und ob die eine der anderen vorgezogen wird und

- empfohlenes “Fanout” (wie die Leiterbahnen die Pins zum Rest der Leiterplatte verlassen).

Anhand dieser Informationen und der Anzahl der Pins können wir zunächst feststellen, ob zwischen den Pins Leiterbahnen verlegt werden müssen. Gehäuse mit 4, 6, 8, 9, 11 oder einer anderen Anzahl von Pins in verschiedenen Anordnungen können geroutet werden, ohne dass eine Leiterbahn zwischen den Pads verlegt werden muss.

Das bedeutet, dass selbst ein normalerweise “schwieriges” BGA mit 0,4 mm Pitch problemlos hergestellt werden kann. Ein BGA mit 0,4 mm Pitch und 0,225 mm Pad-Durchmesser hat zum Beispiel eine Lücke von 0,4-0,225=0,175 mm; wenn man sich die I/OPP-Beschränkungen (Innen-/Außenlage-Pad-zu-Pad) ansieht, ist es möglich, dies mit der Leiterbildklasse 5 zu fertigen.

Zwei Beispiele für BGA-Footprints, die TI empfiehlt. Links ein 6-poliges BGA im 0,4-mm-Raster, das einfach und kostengünstig herzustellen und zu entflechten ist; bei Eurocircuits in der Leiterbildklasse 5, die einen minimalen Pad-zu-Pad-Abstand von 0,175 mm erfordert. Rechts ein Beispiel für ein 11-poliges BGA mit 0,5 mm Pitch und versetzten Pins. Beachten Sie auch, dass TI in beiden Fällen das NSMD-Pad gegenüber dem SMD-Pad empfiehlt.

Höchstwahrscheinlich werden wir Leiterbahnen zwischen den Pads verlegen müssen. Der Trick besteht nun darin, herauszufinden, ob das Bauteil in unserer Anwendung ohne Durchkontaktierungen verwendet werden kann. Dies könnte möglich sein, wenn der Hersteller bei der Platzierung der Pins clever vorgegangen ist. Zum Beispiel indem er zulässt, dass Signale durch andere Pads geführt werden, indem er in bestimmten Bereichen oder an bestimmten Stellen keine Pads vorsieht oder indem er größere Lücken zwischen einigen Reihen oder Spalten vorsieht.

Es könnte auch möglich sein, die Pins auf kreative Weise so zuzuordnen, dass Durchkontaktierungen vermieden werden; dies kann mit der Flexibilität der FPGA-Pin-Zuordnung und mit einigen Mikrocontrollern möglich sein, die konfigurierbare Pin-Zuordnungen haben. Der Verzicht auf Durchkontaktierungen ist ein bedeutender Vorteil, da er eine kostengünstigere Herstellung von Leiterplatten mit Komponenten mit geringerem Abstand ermöglicht.

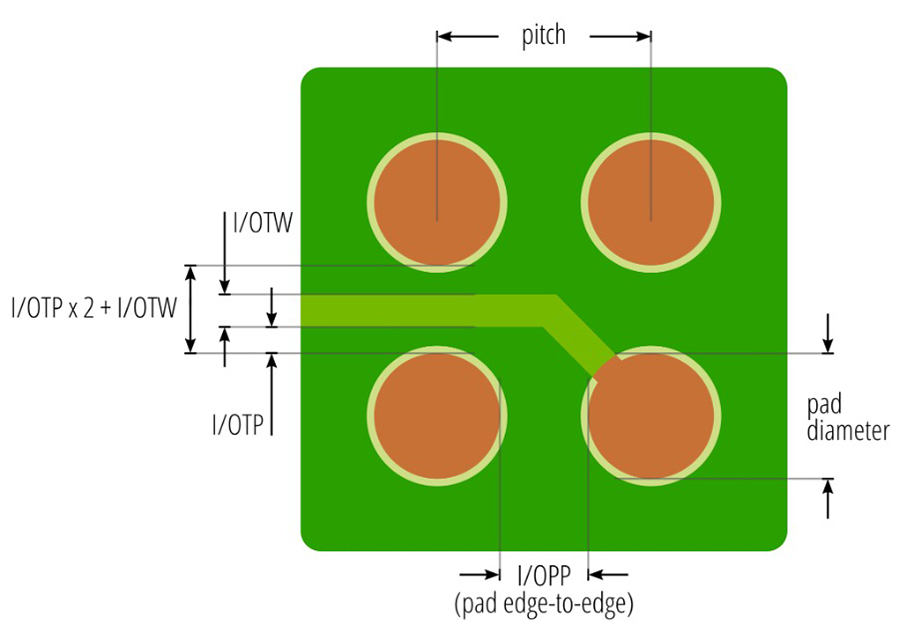

Wenn es uns gelingt, nur mit Leiterbahnen zwischen den Pads auszukommen, müssen wir zunächst den Abstand zwischen den Kanten zweier benachbarter Kupferpads (aus dem Datenblatt des Bauteils) herausfinden. In diesen Abstand müssen wir eine Leiterbahnbreite (TW) und zwei Mindestabstände zwischen den Leiterbahnen und den Pads (TP) unterbringen. Wir sehen uns dann die Anforderungen des Leiterplattenherstellers an, um zu sehen, ob und zu welchen Kosten dies möglich ist.

Die I/OPP legt fest, wie nahe wir Pads innerhalb einer bestimmten Leiterbildklasse platzieren können. Wenn eine Leiterbahn zwischen diesen Pads verlaufen soll, müssen wir zwei I/OTP- und eine I/OTW-Constraints aus derselben Klasse einbauen.

Ein Beispiel: Nehmen wir an, wir haben ein BGA mit 0,65 mm Pitch und einem empfohlenen Pad-Durchmesser von 0,26 mm. Der Abstand zwischen den Kanten der Pads beträgt also

0.65mm – 0.26mm = 0.39mm

Betrachten wir nun die Leiterbildklasse 7 für das Routing der Außenlage:

Outer layer Track Width (OTW) = 0.125mm

Outer layer Track-to-Pad (OTP) = 0.125mm

Der Mindestabstand zwischen den Kanten benachbarter Pads muss also betragen:

Min distance = OTP + OTW + OTP

Min distance = 0.125 + 0.125 + 0.125 = 0.375mm

Es funktioniert!

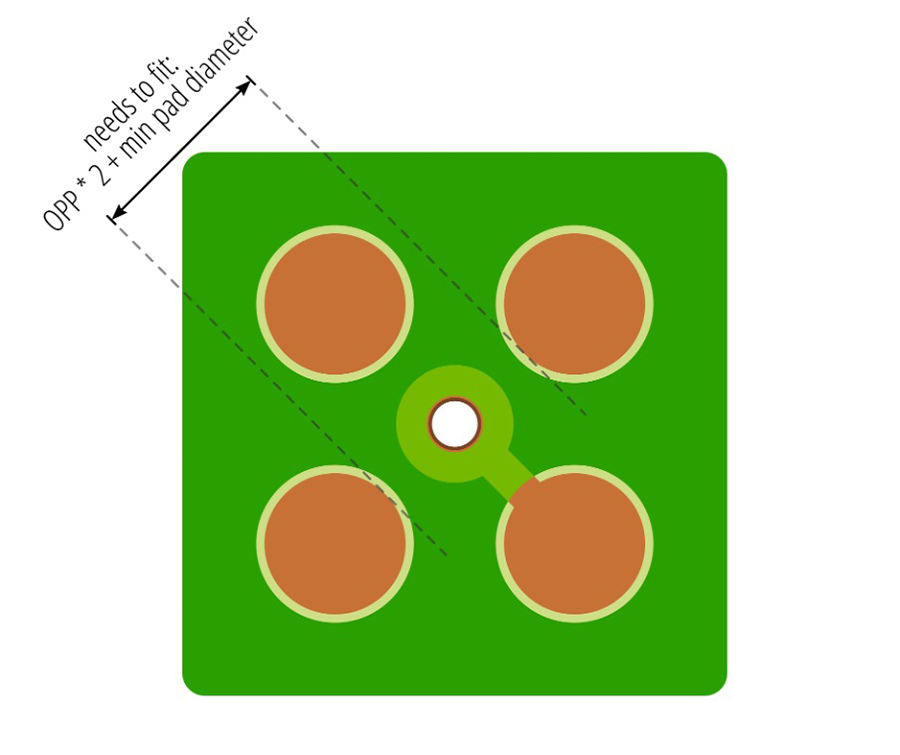

Um herauszufinden, ob wir ein Via zwischen BGA-Pads unterbringen können (Dog-Bone), müssen wir herausfinden, ob das kleinste Via-Pad in den Abstand zwischen den Kanten der diagonalen Pads passt. Hier wird davon ausgegangen, dass das Via zentriert ist; manchmal ist es hilfreich, das Via in Richtung des angeschlossenen Pads zu versetzen. OPP ist der Abstand von Pad zu Pad auf der Außenlage.

Wenn wir tatsächlich Durchkontaktierungen benötigen, kann es etwas komplizierter werden. Beim Dog-Bone sind Vias neben dem BGA-Pad platziert und mit einer kurzen Leitung an das Pad angeschlossen. In der Regel müssen wir zwischen vier BGA-Pads eine metallisierte Bohrung und ein Pad unterbringen. Wir müssen den Abstand zwischen den Kanten der diagonalen Pads ermitteln. Innerhalb dieses Abstands müssen wir zwei Außenlagen Pad-zu-Pad-Abstand (OPP), zwei Außenlagenrestringe (OAR), den fertigen Bohrdurchmesser und die Metallisierung des Bohrlochs (0,1 mm) unterbringen. Für die Klasse 8E haben wir ein Minimum von:

2×0.1 + 2×0.1 + 0.1 + 0.1 = 0.6mm

Für die Klasse 7E haben wir:

2×0.125 + 2×0.125 + 0.1 + 0.1 = 0.7mm

Oder wenn wir den Mindestdurchmesser des Pads für die Musterklasse haben:

2xI/OPP + min pad diameter

Passen diese in den diagonalen Abstand, den wir aus dem Datenblatt haben? Beachten Sie, dass es manchmal unterschiedliche Fertigungsbedingungen für Außen- und Innenlagen gibt, wie in unserer Leiterbildklasse 8. Achten Sie also darauf, wenn dies für Ihr Layout relevant ist.

Lösungsansätze

Da selbst die Verschiebung einer Leiterbahn oder eines Vias um 0,01 mm zu einem höheren Preis führen kann, ist es wichtig, beim Fräsen und Platzieren der Bauteile genau zu sein. Rastertechniken sind entscheidend für die richtige Platzierung.

Erstellen Sie ein oder mehrere Raster, die genau auf die Mittelpunkte zwischen den Pads passen, damit Sie eine Leiterbahn genau in der Mitte verlegen können. Vergewissern Sie sich auch, dass Ihre Leiterbahnbreite tatsächlich den Erwartungen entspricht. Verwenden Sie diese Raster, um Durchkontaktierungen genau zwischen vier Pads zu platzieren. Wenn Sie Durchkontaktierungen in Richtung des angeschlossenen Pads versetzen, können Sie manchmal etwas mehr Platz gewinnen.

Wenn Sie diese Technik verwenden, erstellen Sie ein weiteres Raster für diesen Versatz. Wenn Ihr Werkzeug es zulässt, definieren Sie Randzonen für die BGAs. Wenn Sie sich im Vorfeld die Mühe machen, diese Einstellungen vorzunehmen, sparen Sie später viel Zeit.

Ein Querschnitt eines gefüllten Vias. Das Füllen von Durchsteigern kann eine Routing-Lösung für einige BGAs sein.

Manchmal hilft ein verfülltes Via-in-Pad, um enge Stellen zu umfahren. Dies hat jedoch den Nachteil, dass die Pad-Größe mindestens so groß sein muss wie das Via-Pad. Für die Klasse 8E ist dies ein Durchmesser von 0,4 mm, der größer sein kann, als der vom Bauteilhersteller empfohlene BGA-Pad-Durchmesser. Wenn Sie verfüllte Durchkontaktierungen in Erwägung ziehen, sollten Sie den Preis für den zusätzlichen Schritt des Füllens der Durchkontaktierung gegen den Wechsel zu einer höheren Klassifizierung abwägen; der Preisunterschied könnte erheblich sein. (Mehr zu verfüllten Durchkontaktierungen hier.)

Wir raten zwar davon ab, aber Sie könnten die im Datenblatt angegebene Größe der Pads verringern, um etwas mehr Platz für Leiterbahnen und Durchkontaktierungen zu schaffen. Das könnte funktionieren, wenn Sie nur ein paar Platinen herstellen, ist aber ansonsten ziemlich riskant. Wenn Sie Ihre Platinen bei einem Dienstleister bestücken lassen, müssen Sie ihn auf jeden Fall konsultieren. Bei Eurocircuits fertigen wir die Leiterplatte solange sie unsere üblichen Prüfungen besteht; es sei denn, wir bestücken die Leiterplatte auch für Sie. In diesem Fall wird unser Footprint-Prüfverfahren ein Design mit reduzierten Pads ablehnen und Sie müssen sich mit uns in Verbindung setzen, um zu sehen, ob der Auftrag für die Produktion freigegeben werden kann.

Vielleicht fragen Sie sich jetzt, wie man mit BGAsmit 0,4 mm Pitch mit Hunderten von Anschlüssen entflechten kann? Die Lösung für Bauteile mit 0,5 mm Pitch und feiner ist das HDI-Verfahren (High Density Interconnects). Die HDI-Technik ermöglicht höhere Packungsdichten und verwendet Microvias, die mit einem Laser und nicht mechanisch gebohrt werden. Diese Technologien werden hier nicht betrachtet und sind auch nicht bei Eurocircuits erhältlich.

Praxitipps zum Entflechten von BGA-Layouts

BGAs können unsere Leiterplatten teuer oder kompliziert zu fertigen machen. Mit Praxiswissen und einigen cleveren Manövern können wir etwas dagegen tun. Hier sind meine Vorschläge:

- Verwenden Sie so viele Funktionen wie möglich, wenn Sie die Constraints Ihres Leiterplattenherstellers berücksichtigen;

- Finden Sie die Schwellenwerte für Preis, Funktion und Größe Ihres Herstellers heraus, um Ihre Constraints festzulegen;

- Informieren Sie sich über alle verfügbaren Signal-Fanout-Strategien für Ihr Bauteil;

- Beginnen Sie mit dem größtmöglichen Gehäuse;

- Verwenden Sie unterschiedliche Raster, um sicherzustellen, dass alles genau platziert ist.